#### Министерство образования и науки РФ

Федеральное государственное автономное образовательное учреждение высшего профессионального образования "Казанский (Приволжский) федеральный университет"

#### ИНСТИТУТ ФИЗИКИ КАФЕДРА РАДИОЭЛЕКТРОНИКИ

Специальность: 010801 - Радиофизика и электроника

Специализация: 014204 - Радиоизмерения

# ВЫПУСКНАЯ КВАЛИФИКАЦИОННАЯ РАБОТА НА ТЕМУ: «РАЗРАБОТКА БЛОКА УПРАВЛЕНИЯ ПРИВОДОМ ФОКУСИРОВКИ ТЕЛЕСКОПА РТТ-150»

| Работа з  | завершена:          |                  |

|-----------|---------------------|------------------|

| ""        | 2015 г              | (А.А.Петров)     |

| Работа д  | допущена к защите:  |                  |

| Научныі   | й руководитель      |                  |

| К.ф - м.н | н.,                 |                  |

| доц. каф  | о. радиоэлектроники |                  |

| "_"       | 2015 г              | (Р.И.Гумеров)    |

| Заведую   | ощий кафедрой       |                  |

| Д.ф - м.н | н.,                 |                  |

| доц. каф  | о. радиоэлектроники |                  |

| "_"       | 2015 г              | (М.Н.Овчинников) |

Казань - 2015

#### Оглавление

| Введение                                                                               | 3    |

|----------------------------------------------------------------------------------------|------|

| Глава 1. Обзор инструментальной базы                                                   | 5    |

| 1.1. Принцип работы датчика AVM58                                                      | 5    |

| 1.1.1. Принцип работы абсолютного оптического энкодера                                 | 5    |

| 1.1.2.Интерфейс SSI (Synchronous Serial Interface, синхрон последовательный интерфейс) |      |

| 1.2. Термодатчик ADAM 4015                                                             | 9    |

| 1.3. Конвертор интерфейса ADAM 4520                                                    | 9    |

| 1.4. Электродвигатели СЛ 361/261                                                       | . 10 |

| 1.5. Схема соединения элементов блока фокусировки                                      | . 11 |

| Глава 2. Среда разработки и комплектующие                                              | . 12 |

| 2.1. AVR Studio 4                                                                      | . 12 |

| 2.2.Особенности архитектуры Atmega 128                                                 | . 13 |

| 2.2.1. Таймер счетчик                                                                  | . 15 |

| 2.2.2. USART                                                                           | . 18 |

| 2.3. Реле                                                                              | . 20 |

| Глава 3. Описание устройства управления                                                | . 22 |

| 3.1. Программная часть                                                                 | . 22 |

| 3.1.1.Прерывание по таймеру (опрос датчика)                                            | . 22 |

| 3.1.2. Прерывание по USART (прием передача сигнала СУ)                                 | . 25 |

| 3.1.3. Реализация программы управления моторами на языке ассемблер                     | 29   |

| 3.1.4.Перевод информации из кода Грея в символьный вид ASCII                           | . 34 |

| 3.2. Аппаратная часть                                                                  | .40  |

| ЗАКЛЮЧЕНИЕ                                                                             | . 44 |

| Список литературы                                                                      | .45  |

| Припомение                                                                             | 16   |

#### Введение

**Цель работы**: разработка блока управления приводом фокусировки телескопа РТТ-150.

Актуальность работы заключается в усовершенствовании системы управления телескопом, в повышении надежности работы фокусировки. В предыдущей версии вследствие эксплуатации со временем начали разрушаться провода питающие приводы.

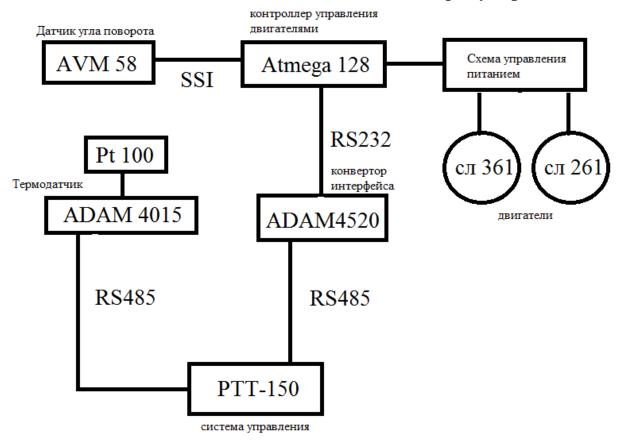

Блок управления привода фокусировки состоит:

- Абсолютного оптического энкодера AVM58.

- Контроллера управления Atmega 128.

- Термодатчика ADAM 4015.

- Конвертор интерфейса RS 432/482 ADAM 4520.

- Релейная схема включения двигателей.

- Электродвигатели СЛ 361/261.

Таким образом, требуется решить следующие задачи:

- Изучить схему абсолютного оптического датчика AVM-58

- Рассмотреть релейные устройства для коммутации питания двигателей

- Написать код для контроллера. При этом нужно, чтобы контроллер управления реализовывал следующие функции:

- Считывание информации о положении энкодера.

- Перекодирование положения из кода Грея в двоичный код.

- Из двоичного кода в ASCII.

- Прием команды по порту USART контроллера от системы управления.

- Разработать релейную схему выполняющую следующие функции:

- Сигнализировать СУ о том в какую сторону движется вторичное зеркало.

- Блокировка работы привода при достижении подвижного блока линзы крайнего положения.

- Реализовать функцию защиты контактов реле при переключении двигателей.

Общий алгоритм изменения фокуса такой:

Контроллер управления с определённой периодичностью считывает информацию о положении энкодера и перекодирует её в символьный вид стандарта ASCII. Из системы управления на контроллер приходит управляющий сигнал с частотой 100 кГц. Контроллер проверят сигнал на наличие ошибок, и в случае обнаружения не выполняет команду. Если же управляющий сигнал правильный, то контроллер проверяет текущее состояние порта схемы управления питание двигателей. При совпадении управляющего сигнала с текущим состоянием контроллер просто отправляет СУ информацию о положении энкодера. При несоответствии текущего состояния выводов с сигналом контроллер либо включает, либо выключает мотор. При подаче первого управляющего импульса с СУ о включении двигателей сначала коммутируется схема реле (выбор двигателя быстро/ медленно, вращение винта влево или вправо), и уже на следующем такте управляющего сигнала СУ (100 кГц) включается питание. Если же подается сигнал о выключение, то в первом такте отключается питание моторов и только при подаче следующего такта пере коммутируется схема реле.

#### Глава 1. Обзор инструментальной базы

#### 1.1. Принцип работы датчика AVM58

#### 1.1.1. Принцип работы абсолютного оптического энкодера

AVM58 относится к классу многооборотных абсолютных оптических энкодеров.

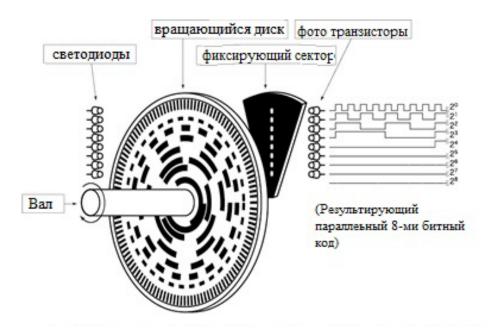

Принцип работы оптических энкодеров:

Свет со светодиодов проходит через кодирующий диск, отверстия в котором проделаны так, что , пропуская или поглощая свет с диодов, кодируют его в код Грея. Далее модулированные пучки попадают на фотодатчик , где преобразуются в электрический импульс. Полученный параллельный электрический импульс поступает на преобразователь, где принимает последовательный вид.

Код Грея удобен тем, что при переходе к следующему или предыдущему по счету числу меняется значение только одного разряда, то есть соседние числа отличаются только по одному разряду. Для цифровых энкодеров- это играет большую роль, так как при изменении положения кодирующего диска информация может быть искажена.

Например при переходе от  $1_{10}$  к  $2_{10}$

0001 к 0010 необходимо изменить и первый бит на 0 и второй бит на 1.

В результате мы имеем два промежуточных значения 0000 и 0011(зависящих от порядка выполнения замены), появление которых создает вероятность ошибочного снятия информации с диска при повороте.

Данная кодировка помогает полностью нивелировать такую погрешность.

Рисунок 1 Принцип работы оптического энкодера

## 1.1.2.Интерфейс SSI (Synchronous Serial Interface, синхронно-последовательный интерфейс)

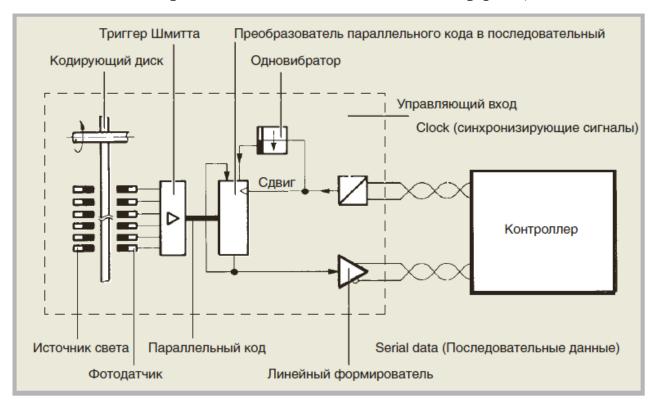

Рисунок 2 Функциональная схема абсолютного датчика на интерфейсе SSI

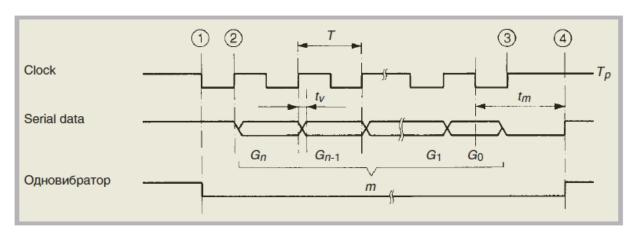

По умолчанию линии передачи (DATA) и синхронизации (Clock) установлены на высоком уровне. Контроллер запрашивает информацию, отправляя управляющий сигнал в виде меандра с периодом Т по линии синхронизации.

Низкий уровень сигнала(1) рис.4 попадает на одновибратор, который в свою очередь отправляет импульс на преобразователь параллельного кода, тем самым фиксируя информацию о положении вала до запроса контроллера.

Далее при переходе синхросигнала на высокий уровень(2) рис.4 с энкодера по последовательной линии данных поступает бит высшего разряда кода Грея.

Последующий низкий уровень синхросигнала обновляет задержку изменения кода положения энкодера, а с приходом следующего высокого уровня отправляется на порядок меньший разряд бит кода Грея.

Данная процедура повторяется до тех пор, пока на контроллер не придет младший бит кода Грея(3)рис.4, и на линии синхросигнала не установится высокий уровень напряжения. Одновибратор перестает обновлять задержку изменения кода и спустя время  $t_m$  разрешает ввод нового параллельного сигнала(4)рис.4.

Условные обозначения:

т — зафиксированный параллельный код;

$t_{\nu}$  — время задержки;

$G_n$  — старший значащий разряд кода Грея;

$G_0$  — младший значащий разряд кода Грея;

T — период синхросигналов;

$t_m$  — время восстановления одновибратора (20 $\pm$ 10 мкс);

$T_p$  — пауза между последовательностями импульсов.

Рисунок 3 Временная диаграмма передачи данных

Для повторной отправки той же кодовой последовательности, необходимо за время восстановления вибратора между(3)и(4) успеть подать еще один синхроимпульс. В случае однооборотного энкодера необходимо отправить 13 импульсов для одноразового сбора данных, и 14 в случае многократного замера одного положения. Для многооборотных энкодеров 25 для одноразового сбора, и 26 для многократного.

Таблица 1 Представление в древовидном формате кода данных для однооборотного и многооборотного датчика

|      |                 |      |     |     |                 |    |         |                |                |                |    |    | S58<br>днооб     | оротн | ый)    | <b>—</b>        | _              | <u> </u>       | <u> </u>       | <u></u>        | <u> </u> | <u> </u>       | Ь.     | _    | <u></u> |    | Ь  | Ь    |         |

|------|-----------------|------|-----|-----|-----------------|----|---------|----------------|----------------|----------------|----|----|------------------|-------|--------|-----------------|----------------|----------------|----------------|----------------|----------|----------------|--------|------|---------|----|----|------|---------|

| AVM: | 58<br>эгообо    | ротн | ый) |     | _               |    | <u></u> | <u>_</u>       | _              | <u></u>        | _  |    | ock (сі<br>гналы |       | -<br>_ | 1               | 2              | 3              | 4              | 5              | 6        | 7              | 8      | 9    | 10      | 11 | 12 | 13   |         |

|      | k (син)<br>алы) | сро- |     | 1   | 2               | 3  | 4       | 5              | 6              | 7              | 8  | 9  | 10               | 11    | 12     | 13              | 14             | 15             | 16             | 17             | 18       | 19             | 20     | 21   | 22      | 23 | 24 | 25   |         |

| Z    | 2 <sup>Z</sup>  |      |     |     |                 |    |         |                |                |                |    |    |                  |       |        |                 |                |                |                |                |          |                |        |      |         |    |    |      |         |

| 12   | 4 096           | 1    | 1   | 211 | 2 <sup>10</sup> | 29 | 28      | 2 <sup>7</sup> | 26             | 25             | 24 | 23 | 22               | 21    | 20     | 2 <sup>11</sup> | 210            | 29             | 28             | 27             | 26       | 2 <sup>5</sup> | 24     | 23   | 22      | 21 | 20 | 0/P* | 4 096   |

| 11   | 2 048           | 1    | 1   | 0   | 2 <sup>10</sup> | 29 | 28      | 2 <sup>7</sup> | 26             | 2 <sup>5</sup> | 24 | 23 | 22               | 21    | 20     | 2 <sup>10</sup> | 29             | 28             | 27             | 26             | 25       | 24             | 23     | 22   | 21      | 20 | 0  | 0/P* | 2 048   |

| 10   | 1 024           | 1    | 1   | 0   | 0               | 29 | 28      | 27             | 26             | 2 <sup>5</sup> | 24 | 23 | 22               | 21    | 20     | 29              | 28             | 27             | 26             | 2 <sup>5</sup> | 24       | 23             | 22     | 21   | 20      | 0  | 0  | 0/P* | 1 024   |

| 9    | 512             | 1    | 1   | 0   | 0               | 0  | 28      | 27             | 2 <sup>6</sup> | 25             | 24 | 23 | 22               | 21    | 20     | 28              | 27             | 26             | 2 <sup>5</sup> | 24             | 23       | 22             | 21     | 20   | 0       | 0  | 0  | 0/P* | 512     |

| 8    | 256             | 1    | 1   | 0   | 0               | 0  | 0       | 27             | 26             | 25             | 24 | 23 | 22               | 21    | 20     | 27              | 2 <sup>6</sup> | 2 <sup>5</sup> | 24             | 23             | 22       | 21             | 20     | 0    | 0       | 0  | 0  | 0/P* | 256     |

| 06   | ороты           |      |     |     |                 | ı  | Іисло   | обор           | отов           |                |    |    |                  |       |        |                 |                |                | -              | Колич          | ество    | отсчё          | тов на | обор | от      |    |    |      | Отсчёть |

Так как сопротивление кабеля связи между контроллером и энкодером создает задержку сигнала, то происходит рассогласование синхросигнала и сигнала данных. Когда сдвиг фаз начинает превышать 180 градусов, начинают возникать ошибки при чтении данных (координаты битов кода не совпадают с моментом считывания)

Близкое расположение контроллера к энкодеру уменьшает импеданс, а значит сдвиг фаз не вносит существенных ошибок.

В таблице представлена зависимость предела скорости передачи данных от длины кабеля.

Таблица 2 Зависимость скорости передачи данных от длины кабеля

| Длина<br>кабеля, м | Максимальная скорость<br>двоичной передачи, кГц (кбод) |

|--------------------|--------------------------------------------------------|

| Менее 50           | 400                                                    |

| Менее 100          | 300                                                    |

| Менее 200          | 200                                                    |

| Менее 400          | 100                                                    |

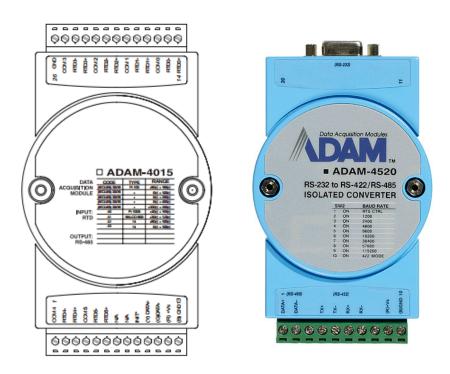

#### 1.2. Термодатчик АДАМ 4015

Фокус системы зависит от показателя преломления среды, а он в свою очередь зависит от температуры. Значит, нам нужно следить за изменением температуры между вторичным и первичным зеркалами. Для этого используется термодатчик Pt100. Сигнал с термодатчика поступает на вход модуля ADAM4015. Поступающая информация обрабатывается встроенным в модуль контроллером и выводится на систему управления через интерфейс RS485.

Рисунок 4 Датчики ADAM 4015|4520

#### 1.3. Конвертор интерфейса ADAM 4520

Большинство компьютеров поддерживают протокол передачи RS 232, а он имеет существенные ограничение по длине линии передачи, скорости

передачи и сетевым возможностям. Интерфейсы RS 432/485 позволяют снять данные ограничения по средствам дифференциальной передачи сигнала. Модуль ADAM-4520 служит конвертором интерфейса между СУ, контроллером управления блока фокусировки и термодатчиком.

#### 1.4. Электродвигатели СЛ 361/261

Электродвигатели СЛ 361/261 являются двигателями постоянного тока последовательного возбуждения. Сначала напряжение подается на якоря, а затем на обмотку возбуждения. Двигатели могут вращаться как в правую сторону, так и в левую. Работает от напряжения 110V

Рисунок 5 Электродвигатель СЛЗ61/261

#### 1.5. Схема соединения элементов блока фокусировки

Рисунок 6 Схема соединения элементов блока фокусировки

#### Глава 2. Среда разработки и комплектующие

#### 2.1. AVR Studio 4

В данной работе средой разработки для контроллера управления фокусировки послужила программа AVR Studio 4. AVR Studio 4 - профессиональная интегрированная среда разработки (Integrated Development Environment - IDE), предназначенная для написания и отладки прикладных программ для AVR микропроцессоров в среде Windows. Написание программы возможно как на языке C, так и на ассемблере. Также IDE поддерживает такие средства разработки для AVR как: ICE50, ICE40, JTAGICE, ICE200, STK500/501/502 и AVRISP. Осуществлена возможность просмотра программы в пошаговом режиме, во время которого изменения состояния регистров контроллера показаны в соответствующем окне.

Присутствует возможность эмуляции аппаратных средств разработки и база данных о периферии каждой модели микроконтроллера

- Watch window: Окно показывает значения определенных символов. В этом окне пользователь может просматривать значения и адреса переменных.

- Trace window: Окно показывает хронологию программы, выполняемой в настоящее время.

- Register window: Окно показывает содержимое регистров. Регистры можно изменять во время остановки программы.

- Memory windows: Окна показывают содержимое памяти программ, данных, портов ввода/вывода и энергонезависимого ПЗУ. Память можно просматривать в НЕХ, двоичном или десятичном форматах. Содержимое памяти можно изменять во время остановки программы.

- I/O window: Показывает содержимое различных регистров ввода/вывода:

- EEPROM

- I/О порты

- Таймеры

- и т.д.

- Message window: Окно показывает сообщения от AVR Studio.

- Processor window: В окне отображается важная информация о ресурсах микроконтроллера, включая программный счетчик, указатель стека, регистр статуса и счетчик цикла. Эти параметры могут модифицироваться во время остановки программы.

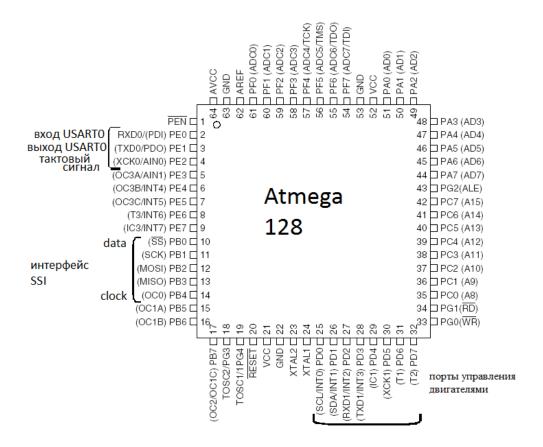

#### 2.2.Особенности архитектуры Atmega 128

Микроконтроллеры AVR относятся к гарвардской архитектуре вычислительной машины (когда информация операндов и команд хранятся в разных участках памяти). Имеют 32 регистра общего назначения размерность 8мь бит.

С регистрами от r16 по r31 можно работать при помощи специальных сложных наборов функций(косвенная адресация, загрузка констант и т.д.).

С регистрами r0- r16 можно работать при помощи специальных операций как с битовыми полями.

Рисунок 7 плата с Atmega 128

Относительно большой объем памяти Flash до 256 Кб; SRAM до 16 Кб; EEPROM до 4 Кб

В зависимости от модели различный набор периферийных устройств среди которых есть:

- Кварцевый генератор;

- Порты ввода вывода;

- Таймеры различной разрядности;

- Универсальный синхронно-асинхронный приемник/передатчик USART;

Задачи, которые должен выполнять контроллер:

- Отправлять синхронизирующий сигнал длиной 25 периодов

- Считывать побитно информацию в виде кода Грея и записывать в озу

- Переводить информацию из кода грея в двоичный код

- Опрос микроконтроллера по синхронно- асинхронному передатчику USART

- Сохранять информацию о состояния блока вкл/ выкл двигателя предыдущего запроса

- Включать или выключать двигатели

- Отправка сообщения о состоянии энкодера Системе Управления (СУ)

Аtmega128 обладает большой периферией устройств, из которой нам понадобится: восьми битный таймер Т0 и универсальный синхронно/асинхронный приемо-передатчик USARTO.

Рисунок 8 Используемые выводы микроконтроллера

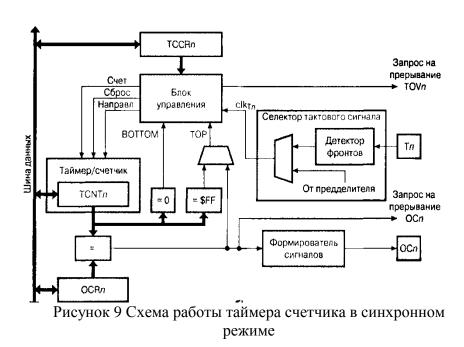

#### 2.2.1. Таймер счетчик

Таблица 3 Таймеры atmega128

| U                                |               |

|----------------------------------|---------------|

| Таймер/счетчик                   | ATmega64x/128 |

| Таймер/счетчик Т0<br>(8-битный)  | •1)           |

| Таймер/счетчик Т1<br>(16-битный) | •             |

| Таймер/счетчик Т2<br>(8-битный)  | •             |

| Таймер/счетчик Т3<br>(16-битный) | •             |

| Таймер/счетчик Т4<br>(16-битный) |               |

| Таймер/счетчик Т5<br>(16-битный) |               |

Таймеры в семействе микроконтроллеров AVR могут выполнять различные функции в зависимости от разрядности и настройки управляющего регистра. В наличии у Atmega128 имеется 4таймера: два 8ми битных и два 16ти битных. Каждый таймер физически привязан к порту ввода-вывода общего назначения, то есть один вывод может выполнять функции и таймера и обычного порта. Для таймера ТО выход схемы сравнения ОСО приурочен к порту РВ4.

управления прерываниями имеется специальный регистр **TIMSK** разрешающий прерывание.1ый или запрещающий ТОІЕ0(разрешает 2ой биты прерывание переполнению) ПО И ОСІЕО(разрешает прерывание по совпадению) настраивают разрешение прерывания для T0. Также имеется регистр флагов прерываний TIFR, который служит сигнализатором события, вызывающего прерывание. 1ый TOV0(флаг по переполнению) и 2ой биты OCF0(флаг по совпадению счетчика) служат для сигнализации о наступлении событий в таймере ТО.

Помимо регистров разрешения прерывания в Т0 имеются:

- управляющий регистр TCCR0

- счетный регистр TCNT0

- регистр сравнения ОСR0

- Регистр синхронно-асинхронного режима ASSR

- Первые три бита регистра управления CS0, CS1, CS2 определяют частоту тактового сигнала(коэффициент предделителя) с которым будет работать таймер.

Таблица 4 Выбор источника тактового сигнала таймера

|      |      |      | Источник такто                                                 | вого сигнала             |                            |

|------|------|------|----------------------------------------------------------------|--------------------------|----------------------------|

| CSn2 | CSn1 | CSn0 | 05                                                             | Асинхронны               | й таймер/счетчик           |

|      |      |      | Обычный таймер/счетчик                                         | ASn = 0                  | ASn = 1                    |

| 0    | 0    | 0    | Таймер/счетчик остановлен                                      | Таймер/счетч             | ик остановлен              |

| 0    | 0    | ı    | clk <sub>I/O</sub>                                             | clk <sub>1/O</sub>       | clk <sub>TOSC1</sub>       |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8                                          | clk <sub>1/O</sub> /8    | clk <sub>TOSC1</sub> /8    |

| 0    | 1    | 1    | clk <sub>I/O</sub> /64                                         | clk <sub>1/O</sub> /32   | clk <sub>TOSC1</sub> /32   |

| 1    | 0    | 0    | clk <sub>I/O</sub> /256                                        | clk <sub>I/O</sub> /64   | clk <sub>TOSC1</sub> /64   |

| 1    | 0    | 1    | clk <sub>I/O</sub> /1024                                       | clk <sub>I/O</sub> /128  | clk <sub>TOSCI</sub> /128  |

| 1    | 1    | 0    | Вывод Тп, счет осуществляется по спадающему фронту импульсов   | clk <sub>I/O</sub> /256  | clk <sub>TOSCI</sub> /256  |

| 1    | 1    | 1    | Вывод Тп, счет осуществляется по нарастающему фронту импульсов | clk <sub>I/O</sub> /1024 | clk <sub>TOSCI</sub> /1024 |

Четвертый WGM01 и седьмой биты WGM00 отвечают за режим работы таймера:

- WGM01=0 ;WGM00=0 нормальный режим.

- WGM01=0; WGM00=1 Phase correct PWM

- WGM01=1 ;WGM00=0 СТС(сброс при совпадении)

- WGM01=1 ;WGM00=1 Fast PWM

Состояние шестого COM01 и пятого битов COM00 определяют сигнал с выхода схемы сравнения OC0= PB4:

- СОМ01=0; СОМ00=0 таймер/счетчик отключен от вывода ОС0

- COM01=0 ; COM00=1 меняется состояние вывода на противоположное

- COM01=1 ; COM00=0 вывод сбрасывается в 0

- COM01=1 ; COM00=1- вывод устанавливается в 1

В режиме СТС (сброс при совпадении ) счетный регистр ТСNТ0 инкрементируется по каждому входящему тактовому импульсу, до тех пор пока величина счетного регистра не станет равной заданной величине в регистре сравнения ОСR0. После счетный регистр сбрасывается в ноль и продолжает счет.

В тот момент, когда счетный регистр TCNT0 равняется регистру сравнения OCR0, устанавливается флаг OCF0 по совпадению счетчика, и если в регистре управления прерываниями TIMSK бит OCIE0 выставлен в единицу, то возможен переход к подпрограмме прерывания.

Одновременно в установкой флага по совпадению счетчика может измениться состояние выхода схемы сравнения ОС0(РВ4), в зависимости от состояния шестого СОМ01 и пятого битов СОМ00 регистра управления ТССR0.

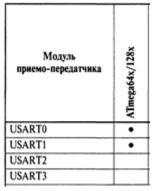

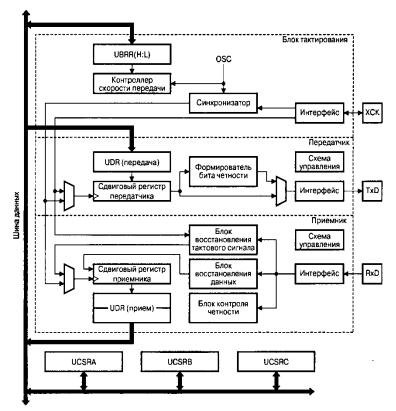

#### 2.2.2. **USART**

USART позволяет передавать и получать информацию по Таблица 5 Приемники последовательной линии данных. Настройка USART Atmega 128

позволяет настроить скорость передачи данных, формат передаваемого пакета данных.

В комплектацию Atmega128 входят два модуля USART. Модули USART способны детектировать ошибки при кодировании, переполнение буфера и неверный стартбит.

Для уменьшения числа ошибок реализована функция фильтрации помех.

Для того чтобы физически контактировать с присылающим или получающим устройством под работу USART выделено три порта вывода общего назначения:

- •Bход USART0 (RXD0) = PE0

- •Выход USART0 (TXD0)= PE1

- •Вход/выход внешнего тактового сигнала (XCK0)= PE2

Для взаимодействия с программой предусмотрены 3 события вызывающие флаг прерывания : «завершение приема данных», «передача завершена», «регистр данных передатчика пуст».

Для временного хранения принимаемых или отправляемых данных (буфер данных) выделен специальный регистр данных UDR0 для USART0.

Для управления состоянием выделено три управляющих регистра UCSR0A, UCSR0B, UCSR0C.

В регистре UCSR0A в основном биты сигнализируют о наступлении, какого то события в модуле и выставляют соответствующий флаг:

- •8ой бит RXC (флаг завершения приема),

- •7ой бит ТХС (флаг разрешения передачи),

- •6ой бит UDRE (флаг опустошения регистра данных),

- •5ый бит FE (флаг ошибки кадрирования),

- •4ый бит DOR (флаг переполнения),

- •3ий бит UPE (флаг ошибки контроля четности),

- •2ой бит U2X ( удвоение скорости обмена),

- •1ый бит МРСМ ( режим мультипроцессорного обмена)

Биты регистра UCSRB устанавливают разрешение на прерывание при наступлении события в модуле USART:

- •8ой бит RXCIE (разрешение прерывания по завершения приема),

- •7ой бит TXCIE (разрешение прерывания по завершении передачи),

- •6ой бит UDRIE (разрешение прерывания при очистке регистра данных UART),

- •5ый бит RXEN (разрешение приема),

- •4ый бит TXEN (разрешение передачи),

- 3ий бит UCSZ2

(формат посылок),

- 2ой бит RXB8 ( 8-й бит принимаемых данных),

- 1ый бит ТХВ8 ( 8ой бит передаваемых данных)

Модуль USART состоит из трех частей: блок тактирования, передатчик и приемник

Скорость передачи задается 12ти разрядным битом UBRR, который

Рисунок 10 Структурная схема модуля USART

физически реализован на двух 8ми разрядных регистрах UBRRH UBRRL.

$$BAUD = \frac{f_{ck}}{16(UBRR + 1)}$$

Для приема/ передачи на скорости 9600 бит/с в регистр UBBR нужно записать 95.

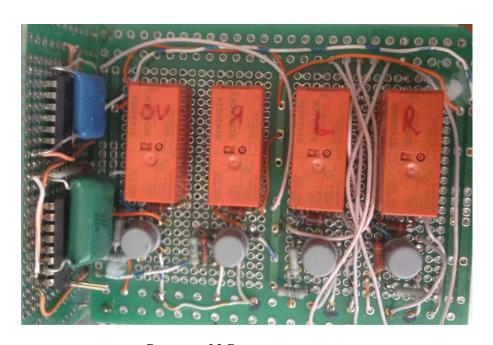

#### 2.3. Реле

Для создания схемы включения питания двигателей нам понадобятся 3 типа реле: pэс-49, RT424024, CRYDOM D4D07.

Герметичное, двухпозиционное, одностабильное реле постоянного тока РЭС49 предназначено для коммутации электрических цепей постоянного и переменного тока. Не нуждается в усилении переключающего сигнала с микроконтроллера.

Для переключения линий в схеме, которая будет под большим напряжением мы будем использовать реле RT424024. Для переключения этих реле нам понадобятся оптроны, усиливающие сигнал с контроллера.

Рисунок 11 реле РЭС-49

Рисунок 12 реле RT424024

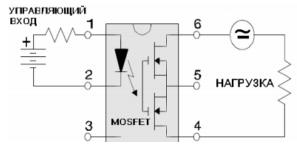

Для подачи тока на возбуждающую обмотку двигателей мы будем использовать оптическое твердотельное реле CRYDOM D4D07

Рисунок 12 твердотельное реле D4D07

Твердотельного реле работает по следующему принципу. Управляющий сигнал попадает на светодиод, где преобразуется в оптический вид. Далее сигнал поступает на светочувствительный затвор полевого транзистора и переключает реле.

Рисунок 134 Принцип работы твердотельного реле

# Глава 3. Описание устройства управления 3.1. Программная часть

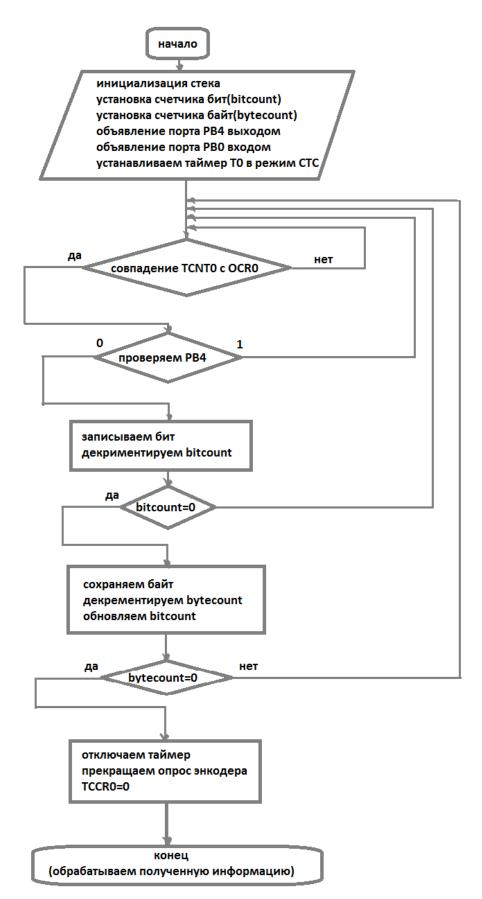

#### 3.1.1. Прерывание по таймеру (опрос датчика)

В первой главе мы познакомились с принципом работы абсолютного оптического энкодера AVM58 и узнали, что для снятия данных нам необходимо подать на вход clock 25 синхро-импульсов (24 для данных и один для стоп бита) с периодом меньше 20 мкс, потому что время обновления одновибратора 30 мкс.

В комплектацию atmega 128 входят четыре таймера/счетчика, два восьми-битных и два 16ти битных. Для генерации нам подойдет один 8ми битный таймер. Настроем его на режим СТС (сброс при совпадении), а в подпрограмме вектора прерывания по сбросу таймера будем считывать линию данных. Для настройки этого режима необходимо в управляющем регистре ТССR0 установить 3ий бит в единицу WGM01=1, а 6ой бит WGM00 =0. Для того чтобы состояние вывода ОС0 менялось каждый полупериод необходимо 5ый и 4ый бит регистра ТССR0 СОМ0 = 01.

Количество тактов после которого происходит сброс таймера задается в регистре OCR0. Формула по который высчитывается частота таймера

$$f_{OCn} = \frac{f_{clk\ I/O}}{2N(1 + OCR_{nx})};$$

где focn-частота таймера, fclk- частота кварца на котором работает контроллер, N-коэффициент деления предделителя.

Перейдем к размерности времени

$$T_{OCn} = T_{clk} 2N(1 + OCR_{nx})$$

При тактовой частоте кварца fclk= 14,744 МГц Tclk= 0,0678 мкс, коэффициент преддделителя N=1, предполагаемый период таймера Tocn=10мкс, следовательно OCR приблизительно

$$OCR_{nx} = \frac{T_{OCn}}{2T_{Clk}} - 1 = 73$$

Инициализировав таймер, опишем работу функции обработки прерывания по таймеру. Блок- алгоритм процесса показан на рис.15

Каждый раз при совпадении счетчика TCNT0 и регистра OCR0 вызывается функция обработки прерывания, в которой проверяется состояние порта PB4 и в случае если PB4=0 с порта PB0 считывается бит данных энкодера и декрементируется счетчик битов. После обнуления счетчика битов в озу контроллера записывается байт и декрементируется счетчик байтов, а счетчик бит обновляется. По обнулению всех счетчиков и байт и бит таймер выключается и прерывания по таймеру не вызываются.

Рисунок 15 Блок схема программы опроса датчика

#### 3.1.2. Прерывание по USART (прием передача сигнала СУ)

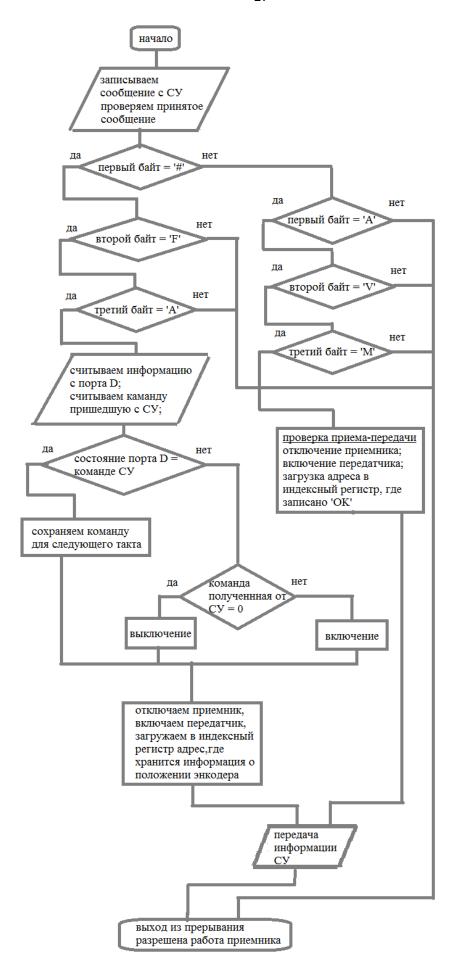

Блок алгоритм процесса изображен на рис.16

При поступление управляющего сигнала с СУ на микроконтроллер, вызывается подпрограмма обработки прерывание по USART.

Управляющее слово СУ состоит из 4 байт, 3 из которых служат для идентификации команды управления приводами, а в последнем байте уже содержится информация о действии. Последний байт содержит информацию о том в какую сторону крутить моторы, быстро или медленно, включить питание на обмотку возбуждения или нет.

При вызове прерывания контроллер включает приемник USART и записывает команду СУ в ОЗУ. После читает последовательно 3 байта и проверяет все ли идентификационные байты на месте. В кодировке ACSII байты представляют следующую комбинацию символов '#FA'.

При несоответствии символов отключаем приемник и выходим из подпрограммы. Если все идентификационные байты на месте, то переходим к считыванию командного байта.

Сравниваем этот байт с текущим состоянием порта D.

При совпадении сохраняем информацию о состоянии выводов порта D для следующего такта. Далее отключаем приемник и отправляем СУ информацию о текущем положении энкодера.

Если же текущее состояние выводов порта D не совпадает с пришедшей командой, то в зависимости от команды принимается решение о включении или выключении моторов.

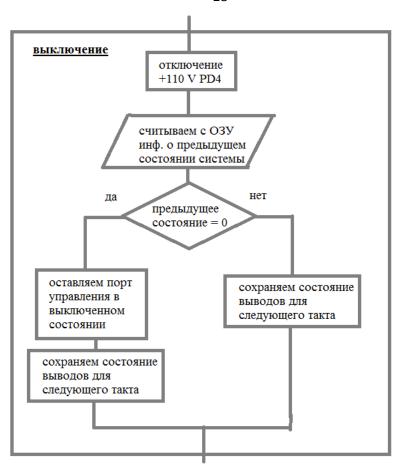

Если команда от СУ =0 значит принимаем решение о выключении моторов.

Сначала отключаем питание на обмотке возбуждения мотора, затем сохраняем информацию о состоянии выводов для следующего такта опроса СУ микроконтроллера , потому что необходимо время для перестройки логики системы защиты после выключения мотора. В противном случае контакты могут обгореть.

При принятии решения о включении моторов сначала коммутируется схема логики на первом такте, а на последующем включается ток на обмотку возбуждения.

После выполнения операций вкл./выкл. контроллер также отправляет сообщение СУ о положении энкодера и выходит из подпрограммы прерывания.

Рисунок 16 Блок схема программы приема/передачи по USART

Рисунок 17 Блок схема включения выключения питания

### 3.1.3. Реализация программы управления моторами на языке ассемблер

```

USART_handler:

; обработка прерывания

in r18,sreg

push r18

clr r18

clr r19

ldi r31,1

ldi r30,16

m5:

sbic ucsr0a,rxc0

rjmp prishlo

sbiw r24,1

breq EndReceive

rjmp m5

prishlo:

in r18,udr0

st z+,r18

inc r19

ldi r25,$09

ldi r24,$20

rjmp m5

EndReceive:

cbi

ucsr0b,rxen0

cpi r19,4

brne ex2

; переход на rjmp, поскольку brne - короткий переход

rjmp nextStep

ex2: rjmp exit2

```

```

; ********проверка принятого кода*********

Если принят неверный код (адрес конторллера), то выход

nextStep:

ldi r30,16

ld r18,z+

ld r19,z+

ld r20,z+ ; 13.03.2015

cpi r18,'#'

;$23

breq verno1

;$41

cpi r18,'A'

breq proverka

cpi r18,'a'

;$61

breq proverka

rjmp exit2

proverka:

cpi r19,'V'

;$56

;проверяем "v"

breq proverka2

;$76

cpi r19,'v'

breq proverka2

rjmp exit2

proverka2:

;$4d

cpi r20,'M'

; проверяем "т"

breq test

cpi r20,'m'

;$6d

breq test

rjmp exit2

verno1:

```

```

cpi r19,'F'

;$46

breq verno2

cpi r19,'f'

;$66

breq verno2

rjmp exit2

verno2:

;$41

cpi r20,'A'

breq privod

;zapros 13.03.2015

cpi r20,'a'

;$61

breq privod

;zapros 13.03.2015

rjmp exit2

privod:

sbi portC,1; установка бита работы системы (100kHz)

ld r20,z

andi r20,$7

in r16,PORTD

com r16

andi r16,$7

ldi r30,0

ldi r31,4

cp r16,r20

; проверка на совпадение с текущим состоянием

breq s1

cpi r20,0

; если нет, то включение или выключение

breq off

rjmp on

off:

sbi portD,4

; выключение: сначала 110V

; выбираем предыдущую команду

ld r16,Z

cpi r16,0

; если не 0, то ждем следующего такта

```

```

brne exit3

com r16

out portD,r16

; обнуляем порт упраления

rjmp exit3

on:

com r20

; включение

out portD,r20

; устанавливаем порт управления без включения 110V

com r20

ld r16,Z

; выбираем предыдущую команду

cpi r16,0

; если 0, то ждем след. такт

breq exit3

cbi portD,4

; иначе вкл. 110v

rjmp exit3

s1:

cpi r20,0

breq exit3

cbi portD,4

com r20

exit3:

cbi portC,1

st Z,r20

; сохраняем команду для след. такта

rjmp zapros

test:

ldi r18,(1<<txen0)

out UCSR0B,r18; отключение приемника, включение передатчика

ldi r30,10

; Запись адреса начального байта($10A) в [Z]

```

```

ldi r31,1

ldi r19,2 ; загрузка счетчика

rjmp transmit

zapros:

ldi r18,(1<<txen0)

out UCSR0B,r18; отключение приемника, включение передатчика

clr r30 ; Запись адреса начального байта($100) в [Z]

ldi r31,1

ldi r19,9; загрузка счетчика

Transmit:

; Ждать очистки буфера передатчика

sbis ucsr0a,udre0

rjmp Transmit

ld r18,Z

out UdR0,r18

dec r19

breq exit

inc r30;inc адреса в [Z]

rjmp transmit

Exit:

m2:

sbis ucsr0a,txc0

rjmp m2

exit2:

ldi r18,(1<<rxcie0) | (1<<rxen0)

UCSR0b,r18

;разрешена работа приемника, разрешено

out

прерывание "прием завершен"

pop r18

out sreg,r18

```

reti

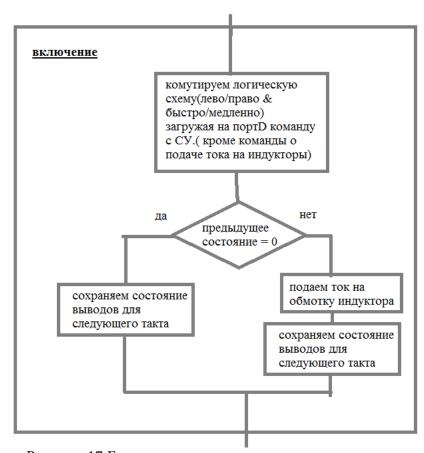

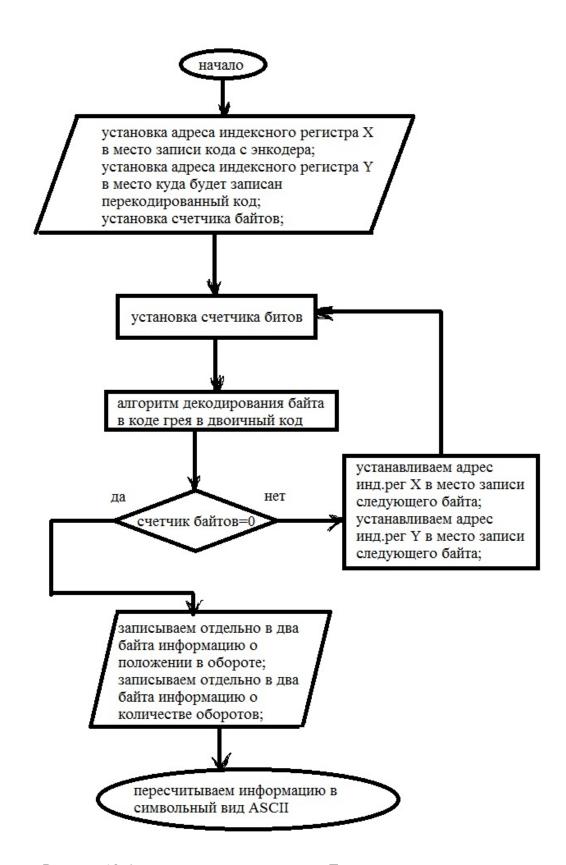

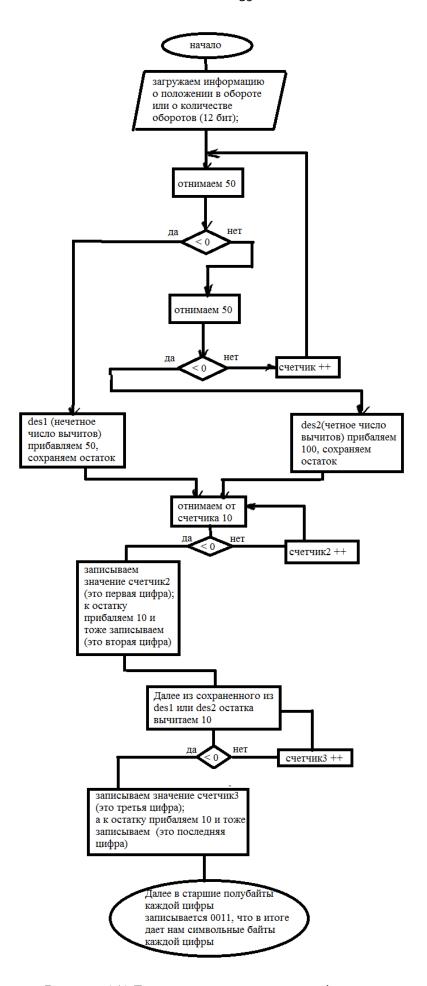

### 3.1.4.Перевод информации из кода Грея в символьный вид **ASCII**

Алгоритм был позаимствован из предыдущей версии программы блока фокусировки. Для начала записанную информацию нужно перевести в двоичный код.

Для перехода из кода Грея в обычный двоичный код используется следующий алгоритм действий.

$$\begin{split} B_k &= \bigoplus_{i=k}^N G_i; \\ B_3 &= \bigoplus_{i=3}^3 G_i = G_3; \\ B_2 &= \bigoplus_{i=2}^3 G_i = G_3 \bigoplus G_3; \\ B_1 &= \bigoplus_{i=1}^3 G_i = G_3 \bigoplus G_3 \bigoplus G_1; \\ B_0 &= \bigoplus_{i=0}^3 G_i = G_3 \bigoplus G_3 \bigoplus G_1 \bigoplus G_0; \end{split}$$

Где  $B_k$ - k-ый бит двоичного кода,  $G_i$ - i-ый бит кода Грея,  $\bigoplus$ - логическая операция «исключающее ИЛИ».

Покажем упрощенный алгоритм нахождения двоичного кода размерностью 4ex бит.

$G_3; G_2; G_1; G_0$  - наш 4ex битный код грея

Умножаем его на маску 1000;

Получим  $G_3$ ; 0; 0; 0 –запомним это число в памяти;

Далее сдвинем маску вправо 0100;

Умножим на код Грея 0;  $G_2$ ; 0; 0

Извлечем из памяти  $G_3$ ; 0; 0; 0

сдвинем вправо 0;  $G_3$ ; 0; 0 и умножим на маску

исключающее или между 0;  $G_2$ ; 0; 0 и 0;  $G_3$ ; 0; 0

даст 0;  $G_3 \oplus G_2$ ; 0; 0 суммируем с предыдущим записанным числом

$G_3$ ;  $G_3 \oplus G_2$ ; 0; 0 и запишем в память

Далее сдвинем маску вправо 0010;

Умножим на код Грея  $0; 0; G_1; 0$

Извлечем из памяти  $G_3$ ;  $G_3 \oplus G_2$ ; 0; 0 сдвинем вправо

0; 0;  $G_3 \oplus G_2$ ; 0 и умножим на маску

исключающее или между 0; 0;  $G_1$ ; 0 и 0; 0;  $G_3 \oplus G_2$ ; 0

даст 0; 0;  $G_3 \oplus G_2 \oplus G_1$ ; 0 суммируем с предыдущим записанным числом

$G_3$ ;  $G_3 \oplus G_2$ ;  $G_3 \oplus G_2 \oplus G_1$ ; 0 и запишем в память

Далее сдвинем маску вправо 0001;

Умножим на код Грея  $0; 0; 0; G_0$

Извлечем из памяти  $G_3$ ;  $G_3 \oplus G_2$ ;  $G_3 \oplus G_2 \oplus G_1$ ; 0 сдвинем вправо

0; 0; 0;  $G_3 \oplus G_2 \oplus G_1$  и умножим на маску

исключающее или между 0; 0; 0;  $G_0$  и 0; 0; 0;  $G_3 \oplus G_2 \oplus G_1$

даст 0; 0; 0;  $G_3 \oplus G_2 \oplus G_1 \oplus G_0$  суммируем с предыдущим числом

$G_3$ ;  $G_3 \oplus G_2$ ;  $G_3 \oplus G_2 \oplus G_1$ ;  $G_3 \oplus G_2 \oplus G_1 \oplus G_0$  и запишем в память

36

Рисунок 18 блок-алгоритм перевода кода Грея в двоичный

Для перекодирования числа в символьный вид стандарта ASCII, необходимо в старший полубайт записать 0011, а в младшем оставить соответствующий числу двоичный код. В итоге получим:

'0' =  $b\ 0011\ 0000 = $30$

'1' = b 0011 0001 = \$31

$2' = b\ 0011\ 0010 = $32$

'3' = b 0011 0011 = \$33

$4' = b\ 0011\ 0100 = $34$

$5' = b\ 0011\ 0101 = $35$

'6' = b 0011 0110 = \$36

$'7' = b\ 0011\ 0111 = \$37$

$8' = b\ 0011\ 1000 = $38$

'9' = b 0011 1001 = \$39

Таблица 6 Символьная кодировка ASCII

| Ь | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9  | Α   | В   | С  | D  | Ε  | ı Fı |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|-----|-----|----|----|----|------|

| 0 | NUL | SOH | STX | ETX | EOT | ENQ | ACK | BEL | BS  | нт | LF  | VT  | FF | CR | S0 | SI   |

| 1 | DLE | DC1 | DC2 | DC3 | DC4 | NAK | SYN | ЕТВ | CAN | EM | SUB | ESC | FS | GS | RS | US   |

| 2 |     | !   |     | #   | \$  | %   | &   | -   | (   | )  | *   | +   | ,  | -  | •  | /    |

| 3 | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9  | :   | ;   | ٧  | =  | ^  | ?    |

| 4 | 9   | Α   | В   | С   | D   | E   | F   | G   | Н   | Ι  | J   | K   | L  | М  | N  | 0    |

| 5 | Р   | Q   | R   | S   | Т   | U   | ٧   | W   | Χ   | Υ  | Z   | ]   | \  | ]  | ^  |      |

| 6 | ,   | а   | b   | С   | d   | е   | f   | g   | h   | i  | j   | k   | l  | m  | n  | 0    |

| 7 | р   | q   | r   | s   | t   | u   | ٧   | W   | Х   | у  | Z   | {   |    | }  | 1  | DEL  |

Максимально возможное четырехзначное число  $2^{12}$  = 4096;

Алгоритм вычислений:

Отнимаем от числа XXXX- 50, инкрементируя счетчик через одно вычитание, до отрицательного числа (до срабатывания в статусном регистре SREG флага C)

При нечетном количестве вычитаний к остатку прибавляем 50. При четном 100. Далее из счетчика отнимаем 10. Получившееся целое- первая цифра четырехзначного числа, а остаток- второе.

Далее из ранее полученного остатка также отнимаем 10. Получившееся целое –третья цифра, а остаток четветое.

Рисунок 149 Блок-алгоритм перевода информации в символьный вид ASCII

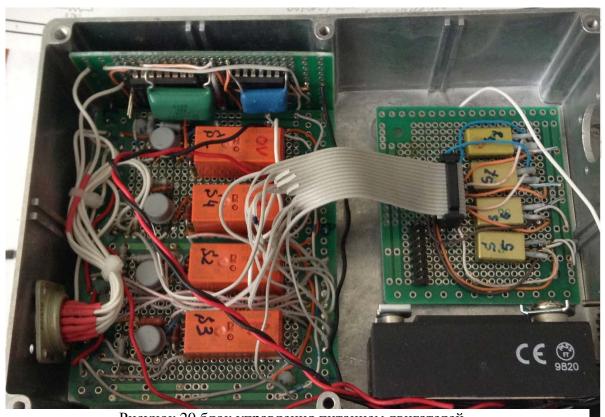

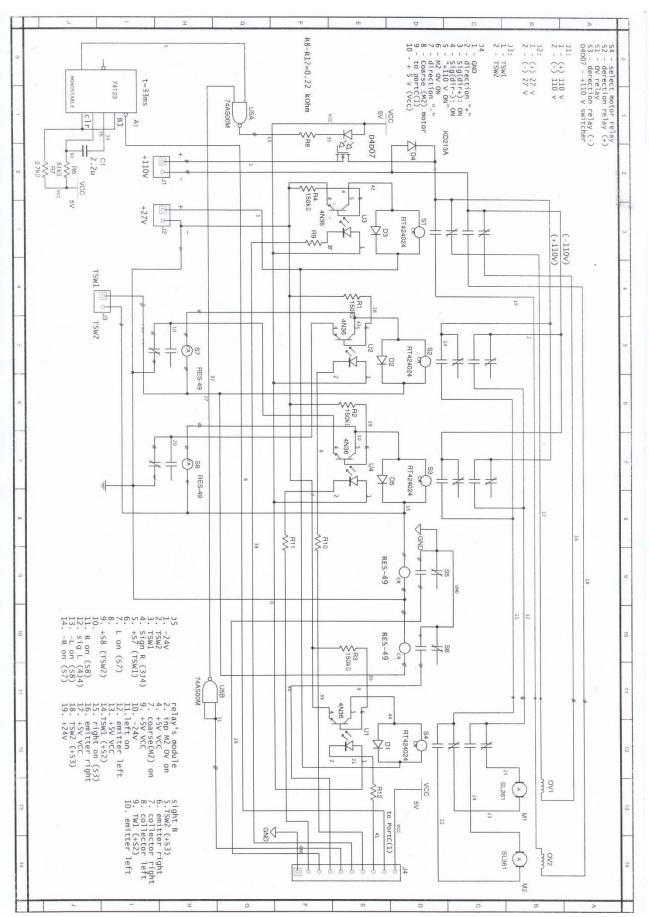

## 3.2. Аппаратная часть

Данная схема необходима для выполнения следующих задач:

- Подача сигнала sig(dir+-) в какую сторону работает мотор.

- При достижении крайнего положения срабатывает концевик, замыкающий реле так, что движение в крайнее положение прекращается и становится возможным движение только в другую сторону.

- Отказ подачи питания моторам, в случае если был подан сигнал о движении и вправо и влево.

- Ток на индукторы мотора не подается до тех пор, пока не собрана схема.

Рисунок 20 блок управления питанием двигателей

Управление логикой схемы осуществляется при помощи сигналов поступающих с порта D микроконтроллера

#### VCC- питание микроконтроллера;

| 0 | VCC             | предотвращающий преждевременное                                            |  |  |  |  |  |

|---|-----------------|----------------------------------------------------------------------------|--|--|--|--|--|

| 0 | port C          | включение обмоток возбуждения моторов                                      |  |  |  |  |  |

| 0 | coarce (M2)     | ; coarce(M2)- выходной сигнал с мк, поступающий на реле переключения якоря |  |  |  |  |  |

| 0 | direction "-" L |                                                                            |  |  |  |  |  |

| 0 | M2 OV           | обмотки;                                                                   |  |  |  |  |  |

| 0 | +110 V          | direction "-" L- вых. сигнал с мк,                                         |  |  |  |  |  |

| 0 | sig(dir-)       | дающий команду крутить мотор влево;                                        |  |  |  |  |  |

| 0 | sig(dir+)       | M2 OV- вых. сигнал с мк,                                                   |  |  |  |  |  |

| 0 | direction"+" R  | поступающий на реле переключения                                           |  |  |  |  |  |

| 0 | GND             | индуктора мотора;<br>+110 V- вых. сигнал с мк, подающий                    |  |  |  |  |  |

port C- выходной сигнал с

питание на индукторы моторов;

Рисунок 21 Выводы схемы защиты J4 Sig(dir-) –сигнал на СУ, оповещающий о том ,что мотор крутится влево;

Sig(dir+)- сигнал на СУ, оповещающий о том ,что мотор крутится вправо;

direction "+" R- вых. сигнал с мк, дающий команду крутить мотор вправо;

При помощи схем из реле рэс-49 реализуется функция блокировки движения линзы по достижению крайнего положения. При приближении вторичного зеркала к краю платформы срабатывают концевые выключатели, переключающие реле так, что движение в крайнюю сторону становится не возможным.

Рисунок 22 Реле защиты и сигнализации на рэс 49

Также эти реле выполняют функцию защиты от подачи ложной команды с системы управления, о движении в обе стороны, и функцию подачи оповещающего сигнала СУ о том в какую строну движется вторичное зеркало.

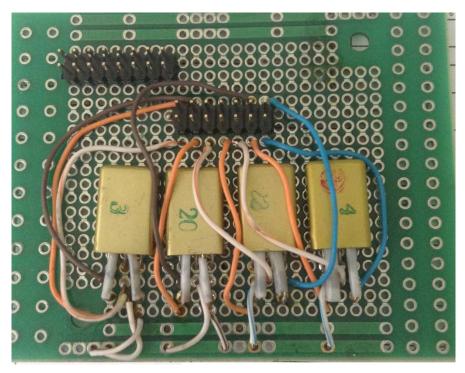

Переключение направления движения блока и переключение двигателей происходит при помощи схемы на реле RT424024. Сигнал с контроллера усиливается при помощи оптронов и переключает реле.

Рисунок 23 Реле коммутации

Ток на обмотку возбуждения поступает с твердотельного реле CRYDOM. Программа написана так, что при включении мотора сначала коммутируется схема переключения двигателей и уже на следующем такте включается двигатель. При выключении сначала отключается питание на двигатель, а на следующем такте формируется схема переключения двигателей.

Так предусмотрена защита же OT зацикливания программы контроллера. Она обуславливается наличием одновидратора, переключающего твердотельное реле. Одновибратор же в свою очередь обновляется за счет отправки сигнализирующего импульса с порта С контроллера. Если что то в программе пошло не так, то сигнал с порта С прекращается, а вместе с ним и прекращается движение вторичного зеркала.

Схема представлена в приложении.

#### ЗАКЛЮЧЕНИЕ

В результате проделанной работы был разработан софт для микроконтроллера:

- Считывающий информацию о положении энкодера.

- Преобразующий информацию о положении из кода Грея в двоичный код.

- Из двоичного кода в ASCII

- Принимающий команды по порту USART от системы управления о включение или выключении мотора, и дальнейшая пересылка СУ информации о положении энкодера.

Также была реализована схема управления питанием двигателей, выполняющая функции:

- Сигнализировать СУ о том в какую сторону движется вторичное зеркало.

- Блокировка работы привода при достижении подвижного блока линзы крайнего положения.

- Реализовать функцию защиты контактов реле при переключении двигателей.

предохраняющая от выпадения вторичное подвижное зеркало и контакты, питающие моторы, от перегорания.

# Список литературы

- 1. Евстифеев А.В. Микроконтроллеры AVR семейства Atmega. / А.В. Евстифеев.-М., 2007.-Гл.2, §2.- С.101-160.

- 2. Белов А.В. Самоучитель по микропроцессорной технике./А.В. Белов.-М.,-2007.- Гл.3. §3.- С.260-300.

- 3. Жданкин,В.К. Абсолютные датчики углового положения с интерфейсом SSI/ Жданкин В.К. // Современные технологии Автоматизации.-2004.-№4.-С.35-47.

- 4. Нарышкин А.К. Цифровые устройства и микропроцессоры/ А. К. Нарышкин. –М.,-2006.-Гл.18 С.252-260.

- 5. К. Фрике Вводный курс цифровой электроники/ К. Фрике.-М.,2003.-Гл.1,§2.- С.19-32.

- 6. Дьяков А.Ф. Основы проектирования релейной защиты электроэнергетических систем./ Платонов В.В., Дьяков, А.Ф.–М.: МЭИ, 2000.- 55с.

- 7. Гуричев В.И. Первый международный стандарт на твердотельные реле/ Гуричев В.И //Электричество.-2009.-№4.-С.54-60.

### Приложение

```

**

; * Опрос датчика по общему порту ввода/вывода PORT В (протокол SSI)

* тактовый сигнал считывания clk encoder выдается через вывод PB4

* сигнал данных от датчика приходит на вывод РВО

; * частота опроса 100 КГц.

; * Данные выдаютса через USART0 в асинхронном режиме,

; * со скоростью 9600 Baud.

.include

"m128def.inc"

.cseg ; переход на собственно код программы

. ************

; * Interrupt vectors

.org 0

jmp

begin; Reset вектор

.org $1e

jmp

timer_handler

.org $24

jmp usart_handler

; ТЕЛО ОБРАБОТКИ ПРЕРЫВАНИЯ ПО ТАЙМЕРУ(ОПРОС ДАТЧИКА)

timer_handler: ; тело прерывания по таймеру

```

```

mov r14,r16

in r16,PINC

eor r16,r14

out PORTC, r16

brtc M1

clt

rjmp propusk

M1: in

r16,PINB

sbrc r16,4; проверка состояния вывода PB4

rjmp Propusk; если 0 то считываем бит

read_bit:

r16,PINB

in

andi r16,1; выделение бита данных encodera

r17,r16; сохранение бита данных encodera

or

r20

dec

breq save byte; если байт набран то сохраняем его

1s1

r17

clz

rjmp propusk

save_byte:

Z+,r17

st

clr

r17

r20,8

ldi

dec

r21

```

```

brne propusk

set

Propusk:

reti

; обязательно reti, а не просто ret

; иначе флаг разрешения прерываний не установится и больше

; никакие прерывания вызываться не будут

**************************

******

ОБМЕН ПО ПОРТУ USARTO

*************************

******

USART_handler: ; обработка прерывания

in r18, sreg

push r18

clr r18

clr r19

ldi r31,1

ldi r30,16

13.03.2015

in r18,udr0

st z+,r18

inc r19

```

```

ldi r25,$09

ldi r24,$20

m5:

sbic ucsr0a,rxc0

rjmp prishlo

sbiw r24,1

breq EndReceive

rjmp m5

prishlo:

in r18,udr0

st z+,r18

inc r19

ldi r25,$09

ldi r24,$20

rjmp m5

EndReceive:

cbi

ucsr0b,rxen0

cpi r19,4

; переход на rjmp, поскольку brne - короткий переход

brne ex2

rjmp nextStep

ex2: rjmp exit2

; ********проверка принятого кода********

Если принят неверный код (адрес конторллера), то выход

nextStep:

ldi r30,16

ld r18,z+

ld r19,z+

ld r20,z+ ; 13.03.2015

cpi r18,'#'

;$23

```

|       | breq verno1     |                   |                 |

|-------|-----------------|-------------------|-----------------|

| ;     | <br>cpi r18,'A' | ;\$41             |                 |

|       | breq proverka   | , ,               |                 |

|       | cpi r18,'a'     | ;\$61             |                 |

|       | breq proverka   |                   |                 |

|       | rjmp exit2      |                   |                 |

| prove |                 |                   |                 |

|       | cpi r19,'V'     | ;\$56             | ;проверяем "v"  |

|       | breq proverka2  |                   |                 |

|       | cpi r19,'v'     | ;\$76             |                 |

|       | breq proverka2  |                   |                 |

|       | rjmp exit2      |                   |                 |

| prove | erka2:          |                   |                 |

|       | cpi r20,'M'     | ;\$4d             | ; проверяем "m" |

|       | breq test       |                   |                 |

|       | cpi r20,'m'     | ;\$6d             |                 |

|       | breq test       |                   |                 |

| ;     |                 |                   |                 |

|       | rjmp exit2      |                   |                 |

| verno | 01:             |                   |                 |

|       | cpi r19,'F'     | ;\$46             |                 |

|       | breq verno2     |                   |                 |

|       | cpi r19,'f'     | ;\$66             |                 |

|       | breq verno2     |                   |                 |

|       | rjmp exit2      |                   |                 |

| verno | 02:             |                   |                 |

|       | cpi r20,'A'     | ;\$41             |                 |

|       | breq privod     | ;zapros 13.03.201 | 5               |

|       | cpi r20,'a'     | ;\$61             |                 |

sbi portC,1; установка бита работы системы (10Hz)

ld r20,z

andi r20,\$7

in r16,PORTD

com r16

andi r16,\$7

ldi r30,0

ldi r31,4

ср r16,r20 ; проверка на совпадение с текущим состоянием

breq s1

срі r20,0 ; если нет, то включение или выключение

breq off

rjmp on

off:

sbi portD,4 ; выключение: сначала 110V

ld r16,Z ; выбираем предыдущую команду

срі r16,0 ; если не 0, то ждем следующего такта

brne exit3

```

com r16

; обнуляем порт упраления

out portD,r16

4

rjmp exit3

on:

com r20

; включение

out portD,r20

; устанавливаем порт управления без включения 110V

com r20

ld r16,Z

; выбираем предыдущую команду

cpi r16,0

; если 0, то ждем след. такт

breq exit3

cbi portD,4

; иначе вкл. 110v

rjmp exit3

s1:

cpi r20,0

breq exit3

cbi portD,4

com r20

exit3:

cbi portC,1

st Z,r20

; сохраняем команду для след. такта

rjmp zapros

```

test:

```

1 di r18, (1 < txen0)

out UCSR0B,r18; отключение приемника, включение передатчика

; Запись адреса начального байта($10A) в [Z]

ldi r30,10

ldi r31,1

ldi r19,2 ; загрузка счетчика

rjmp transmit

zapros:

ldi r18,(1<<txen0)

out UCSR0B,r18; отключение приемника, включение передатчика

clr r30 ; Запись адреса начального байта($100) в [Z]

ldi r31,1

ldi r19,9; загрузка счетчика

Transmit:

; Ждать очистки буфера передатчика

sbis ucsr0a,udre0

rjmp Transmit

ld r18,Z

out UdR0,r18

dec r19

breq exit

inc r30;inc адреса в [Z]

rjmp transmit

```

Exit:

```

m2:

sbis ucsr0a,txc0

rjmp m2

sbi ucsr0a,txc0; ??????!!!!

exit2:

ldi r18,(1<<rxcie0) | (1<<rxen0)

out UCSR0b,r18; разрешена работа приемника, разрешено

прерывание "прием завершен"

pop r18

out sreg,r18

reti

; ПРОЦЕДУРА ПЕРЕВОДА В ДЕСЯТИЧНЫЙ ВИД

peres4et:

clr r16

clr r17

clr r18

clr r19

1:

sbiw r24,50

brcs des1

sbiw r24,50

```

```

brcs des2

inc r17

rjmp 1

des1:

adiw r24,50

clc

mov r19,r24

rjmp L2

des2:

adiw r24,50

adiw r24,50

clc

mov r19,r24

L2:

subi r17,10

brcs L3

inc r16

rjmp L2

L3:

subi r17,-10

clc

L4:

subi r19,10

brcs L5

inc r18

rjmp L4

L5:

subi r19,-10

```

```

clc

ret

; ОСНОВНАЯ ПРОГРАММА

begin:

; инициализация стека

ldi

r16,low(RAMEND)

out

spl,r16

r16,high(RAMEND)

ldi

out

sph,r16

; объявление вывода порта выходом

ldi

r16,(1<<4)

DDRB,r16

out

-----13.03.2015 порт для управления приводами

;(0-й бит для индикации работы

программы)

ldi

r16,$1f

DDRd,r16

out

ldi

r16,$1f

out portD,r16

ldi

r16,3

DDRC, r16

out

; начальное состояние линии clk encoder Высокий уровень

```

r16,(1<<4)

ldi

```

portb,r16

out

nop

; задержка для обеспечения нужной длительности сигнала IDLE

r16,160

ldi

m3: dec r16

brne m3

;***для test пишем OK***

ldi r30,10

ldi r31,1

;$4f

ldi r16,'O'

st z+,r16

ldi r16,'K'

;$4b

st z,r16

; Настройка режима работы USART0

ldi

r16,0x6

sts ucsr0c,r16

; Настройка скорости обмена USART0

ldi r16,0

sts ubrr0h, r16

ldi r16,95

out ubrr0l,r16; скорость обмена 9600 Baud

;****Отсчеты****

Schitivanie_fokusa:

```

```

ldi r21,3 ; счетчик байтов

ldi

r20,9; счетчик циклов (битов)

clr

r31 ; загрузка в индексный регистр [Z] адреса r1

ldi

r30,1

; запуск таймера

ldi

r16,0

; остановить таймер на период инициализации

TCCR0,r16

out

; сброс счетчика

ldi

r16,0

TCNT0,r16

out

ldi

r16,$49; загрузка маски сравнения 73 машинных цикла

OCR0,r16

out

ldi

r16,(1 << 3) \mid (1 << 4); clk T0 = clk i/o = 14,744Mhz;

TCCR0,r16;

режим работы СТС; ОС0-менять на

out

противоположный

ldi r16,(1<<3) | (1<<4) | (1<<0)

out tccr0,r16; пуск

r16,(1<<1)

ldi

out

TIMSK,r16; разрешение прерывания по совпадению

таймера Т0

;общее разрешение прерываний

```

sei

```

clr r1

clr r2

clr r3

clr r17

; цикл

forever:

r21,r21; проверка r21

brne forever

forever

brts

; если r21=0 то есть сохранили 3 байта, то:

; остановка таймера

ldi

r16,0

TCCR0,r16

out

; разрешение прерывания от USART 0

ldi r18,(1<<rxcie0) | (1<<rxen0)

out UCSR0B,r18; разрешена работа приемника, разрешено

прерывание "прием завершен"

:----

com r1

com r2

com r3

; ****декодирование Gray - Binary: ****

clr r27 ; загрузка адрес регистра r1 в [X]

r26,1

ldi

clr

r29

```

```

ldi

r28,5; и регистра r5 в [Y]

r16,3

ldi

mov r9,r16 ; счетчик байтов

clr r15

clt

Decode_byte:

r16,$80

ldi

mov r0,r16; маска 10000000

r16,7

ldi

mov r8,r16; счетчик битов

r4,X;(r1,r2,r3)

ld

and r4,r0

r15,r4

or

brtc m6

ldi

r16,$80

r15,r16

eor

m6:

Y,r15

st

loop1:

lsr

r0

ld

r4,X;(r1,r2,r3)

and r4,r0

ld

r16,Y;(r5,r6,r7)

lsr

r16

r16,r0

and

r16,r4

eor

r15,r16

or

Y,r15

st

dec

r8

```

```

brne loop1

; следующий байт:

sbrc r15,0

set

clr r15

dec

r9

breq dalshe

inc r26; установка r2,r3

inc r28; установка r6,r7

rjmp decode_byte

Dalshe:

clt

; ****** определение числа оборотов и положения в обороте ****

r16,r6

mov

andi r16,$f

r12,r16

mov

r13,r7; в регистрах r12,r13 хранится положение в тек. обороте

mov

r16,r6

mov

swap r16

andi r16,$f

swap r5

mov r17,r5

andi r17,$f0

r16,r17

or

r17,r5

mov

andi r17,$f

```

r10,r17

mov

```

r11,r16; в регистрах r10,r11 хранится число оборотов

mov

; запрет прерывания от USART0 на время обновления данных и опроса

датчика

ucsr0b,rxcie0

cbi

; *****Перевод в десятичный и символьный вид (в ASCII коды) *****

mov r25,r10

mov r24,r11

rcall peres4et

ldi r20,$30

ldi r31,1

clr r30

add r16,r20

add r17,r20

add r18,r20

add r19,r20

st Z+,r16

st Z+,r17

st Z+,r18

st Z+,r19

ldi r16,$3a

st z+,r16

mov r25,r12

mov r24,r13

rcall peres4et

add r16,r20

```

add r17,r20

add r18,r20

add r19,r20

st Z+,r16

st Z+,r17

st Z+,r18

st Z+,r19

jmp schitivanie\_fokusa

Рисунок 24 Схема питания двигателей СЛ 361/261