## МОДЕРНИЗАЦИЯ УЗЛОВ БЛОКА УПРАВЛЕНИЯ ИОНОЗОНДА «ЦИКЛОН». PCI УПРАВЛЯЕМЫЕ УЗЛЫ СИНТЕЗАТОРА ЧАСТОТ И БУФЕРНОЙ ПАМЯТИ

И.А. Зюзько, В.П. Бабин, А.Д. Акчурин, Д.Ф. Хасанов

Казанский Федеральный Университет, 420008, г. Казань, ул. Кремлёвская, 18

E-mail: zyuzko.ivan@gmail.com

**Аннотация.** Для улучшения качества зондирования (разрешающую способность по высоте и скорость зондирования) и возможности исследовать быстротекущие ионосферные процессы была поставлена задача по модернизации ионозонда, работающего на кафедре радиоастрономии в данный момент. В работе представлены разработанные узлы хранения и синтеза частот для проекта модернизации ионозонда.

**Ключевые слова:** ионозонд; SDRAM; контроллер памяти; синтезатор частот; DDS; ПИВ

## MODERNIZATION OF COMPONENTS OF THE CONTROL UNIT OF THE IONOSONDE “ЦИКЛОН”. PCI CONTROLLED NODES OF FREQUENCY SYNTHESIZER AND BUFFER MEMORY

I.A. Zyuzko, V.P. Babin, A.D. Akchurin, D.F. Khasanov

**Abstract.** In order to improve the quality of sounding (height resolution and speed of sounding) and the ability to study fast ionospheric processes, the task of modernization of the ionosonde working at the department of radioastronomy at the moment was set. The paper presents the developed components of storage and frequency synthesis for the project of modernization of the ionosonde.

**Keywords:** ionosonde; SDRAM; memory controller; frequency synthesizer; DDS; TID

### Введение

Ионозонд, который используется в настоящее время кафедрой радиоастрономии для зондирования ионосферы, построен на основе микросхемы ПЛИС (Программируемые Логические Интегральные Схемы) малой степени интеграции MAX II от Altera. Она содержит 1270 логических блоков и не способна включать в себя большое количество внешних устройств, необходимых для работы, таких как GPS-часы, память, АЦП и т.д. Это не только ведёт к неудобству эксплуатации, но и не позволяет повысить разрешающую способность по высоте и скорость зондирования. В то же время данные параметры крайне необходимы для исследования быстротекущих событий, таких как, например, перемещающиеся ионосферные возмущения (ПИВ).

Все вышеперечисленные недостатки и быстрое развитие элементной базы привело к возможности и необходимости модернизации ионозонда и реализации всех управляющих блоков на одной плате. Это позволит не только повысить эксплуатационную надёжность (что также повышает неприхотливость в обслуживании) из-за потери контактов в многочисленных разъёмах, но и избежать ошибок в передаче и задержке данных между ПК и платой управления. Такие протоколы обмена данными, как Ethernet и USB, будут давать ошибки из-за наличия рядом мощного передатчика. По этой причине главной шиной обмена была выбрана PCI (Peripheral

Общая идеология проекта по модернизации ионозонда заключается в том, что обработка данных сводится к минимуму на уровне HDL-прошивки. Это позволит почти полностью избежать последующие реконфигурации низкоуровневого оборудования с возможностью изменения алгоритма обработки данных прямыми из операционной системы.

Для обеспечения работоспособности всех узлов (таких как АЦП, привязка ко времени, синтезатор частот, буфер памяти) необходимо использовать микросхемы ПЛИС с большим количеством логических элементов и средней степенью интеграции. В свою очередь, такая микросхема, как Cyclone IV, установленная на новой плате блока управления ионозонда, помимо большого количества логических блоков (25 тысяч), содержит встроенную памятью объёмом в среднем 1 Мбит и большое количество пользовательских входов/выходов.

**Секция 1. Дистанционное зондирование верхней атмосферы, ионосфера и космического пространства**

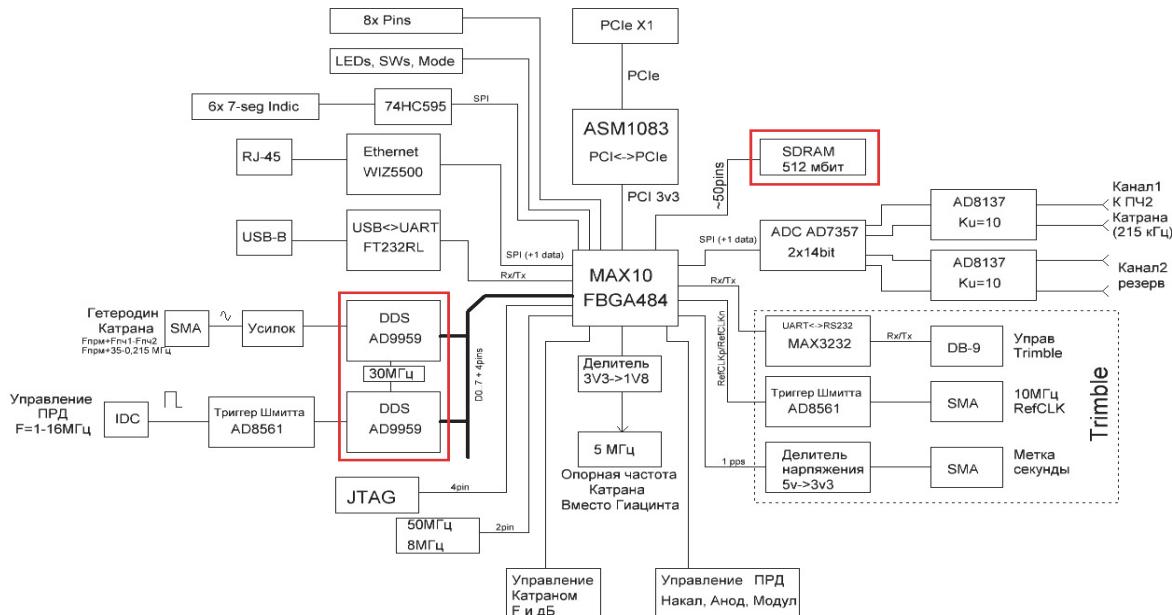

Написание прошивки на HDL Verilog производилось для платы управления ионозонда (на которой находится ПЛИС Cyclone IV), разработанной Хасановым Д.Ф. и названой Wincent. Блок-схема разрабатываемых в статье узлов платы представлена на рис. 1. Как видно из рисунка, в плате заложено большое количество возможностей, и написание HDL-кода для такой платы сразу и целиком чрезвычайно сложно. Поэтому на данном этапе работы было реализовано лишь два PCI-управляемых устройства: узел синтезатора частот (DDS, Direct Digital Synthesizer) [1] и буферная SDRAM память (для хранения отсчетов АЦП), которые выделены красными прямоугольниками на блок-схеме. HDL-код тестиировался на отладочном комплекте DE0-CV. Он содержит такую же микросхему памяти и расширения для синтезатора, что и на целевом устройстве, а также содержит больше логических блоков. Данный подход упрощает разработку. Впоследствии при переносе блоков на плату Wincent необходимо будет только заменить входы/выходы, следуя топологии печатной платы.

Рис. 1. Блок-схема платы Wincent

### PCI-управляемая буферная память на микросхеме SDRAM.

В качестве памяти использовалась микросхема IS42S16320D объемом 512 Мбит [2].

Для ускорения разработки различных объемных задач существуют готовые IP-ядра, которые базируются на шине Avalon (в том числе и контроллер SDRAM) для унификации взаимодействия их друг с другом и с soft-процессором Nios. Для их размещения необходимо большое количество логических блоков. В то же время глобальной HDL прошивке также необходимы свободные логические блоки под узлы для управления PCI и АЦП, DDS и т.д. Это делает невозможным использование уже готовых IP-ядер.

HDL-код из открытых источников обеспечивает лишь одиночное чтение или одиночную запись [3]. Для взаимодействия с PCI шиной требуется пакетный режим (это также позволит повысить скорость передачи данных). Учитывая все недостатки уже готовых решений, была поставлена задача по реализации контроллера (блока управления) SDRAM-памяти.

В предыдущих этапах работы была реализована поведенческая Verilog модель блока контроллера микросхемы SDRAM в среде ModelSim. Необходимость в этом возникла из-за сложности прошивки и специфики памяти, которая требует обновления (регенерации, англ. refresh) каждые 64 мс [2]. Взаимодействие с микросхемой происходит по сложному протоколу команд (каждый этап обращения к памяти требует выставления определенных команд и строго привязанный по времени ответ на них со стороны контроллера). Для отладки общей структуры проекта намного проще создать поведенческую модель контроллера и впоследствии оптимизировать HDL-код под плату Wincent.

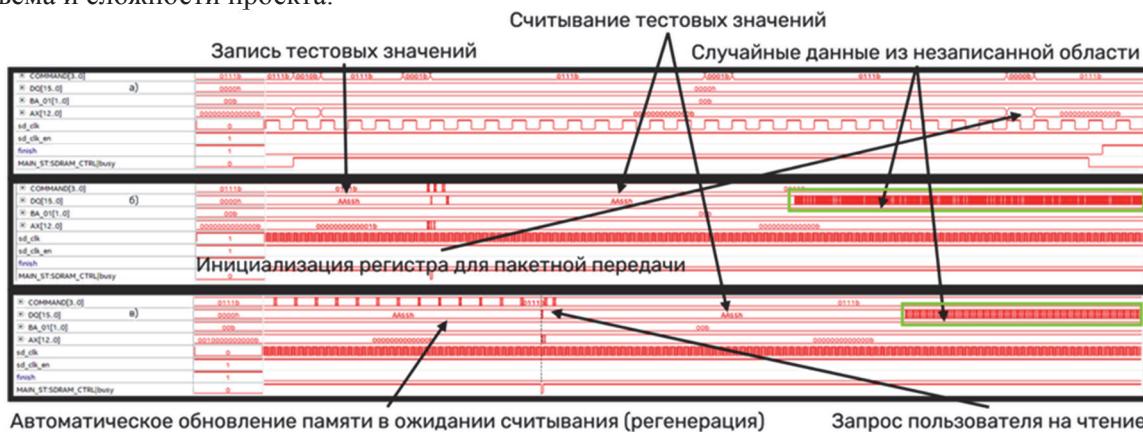

После тестирования и отладки модели, написанной в среде ModelSim, была аппаратно реализована прошивка. Временные диаграммы основных этапов работы с памятью для аппаратной реализации контроллера представлены на рис. 2. Главные особенности контроллера:

- Количество использованных логических блоков с учетом отладочных составило 750 (4% от общего количества логических блоков на Cyclone V);

- Реализация обладает малым количеством управляемых сигналов, что упрощает взаимодействие с памятью.

Мы смогли достичь стабильной работы без ошибок на 50 МГц. В дальнейших работах частоту необходимо будет повысить до предельной (200 МГц) для увеличения пропускной способности всей системы.

В данном проекте отсутствуют режимы одиночной записи и одиночного чтения (присутствует только пакетный режим), и унифицированная шина для взаимодействия с другими узлами, так как нет необходимости в такого типашине, которая привела бы к увеличению общего объема и сложности проекта.

Рис. 2. Временные диаграммы а) процесса инициализации памяти в пакетном режиме;

б) чтения и последующей записи без обновления памяти;

в) чтения и записи с произвольным ожиданием между ними

#### PCI-управляемый DDS синтезатор AD9959.

В новой версии ионозонда используется усовершенствованный DDS синтезатор, принципы работы которого изложены в работе [4]. В предыдущей версии использовался DDS синтезатор AD9851, который имел существенный недостаток: для изменения частоты требовалась полная перезагрузка управляющего слова, что занимало порядка 200 мкс и не позволяло быстро переключаться между импульсами.

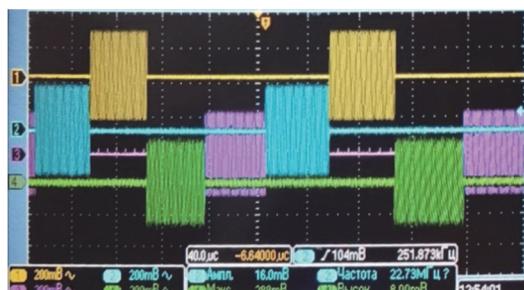

DDS синтезатор AD9959, расположенный на плате Wincent, лишен этого недостатка, так как поддерживает 16 предварительно загруженных «профилей» (управляющих слов) частот, между которыми можно мгновенно переключаться, подавая соответствующий номер (0–15 в двоичном виде) на управляющие входы P0–P3 [4]. Кроме того, AD9959 содержит четыре независимых DDS-ядра, что позволяет генерировать сигналы на четырех частотах одновременно, что может позволить радикально сократить время зондирования. На рис. 3 разными цветами (на разных каналах осциллографа) для наглядности приведена реализация переключения частот между 4 ядрами последовательно.

Рис. 3. Пример реализации последовательного синтеза частот длительностью по 50 мкс в четырёхъядерном режиме

Для загрузки профилей в DDS синтезатор используется ПЛИС. Архитектура прошивки включает два основных модуля: State-machine и SPI. SPI-модуль обеспечивает передачу данных по интерфейсу SPI. По данному протоколу происходит загрузка управляющих слов в микросхему. State-machine (конечный автомат) – критически важный модуль, так как корректная работа DDS возможна только при правильном заполнении регистров профилей. Его настройка была выполнена строго по документации от Analog Devices [4].

Для наглядности, переключение можно разделять паузами между импульсами (для одного ядра DDS). В связи с этим использовался вывод PWR\_DWN\_CTL, который позволяет отключать питание цифровой логики и ЦАП в промежутках между импульсами.

Для того, чтобы иметь возможность загружать значения регистров микросхемы без перепрограммирования ПЛИС, была реализована встроенная память, содержащая все используемые значения регистров, которые смогут меняться программно. Это позволяет изменять настройки профилей без внесения правок в код прошивки, что значительно упрощает настройку системы. В перспективе аналогичный подход, вероятнее всего, будет применен для работы с PCI-портом через реализацию RAM-памяти.

#### **Перспективы: одновременная генерация на четырех частотах**

Поскольку AD9959 поддерживает одновременную генерацию на четырех ядрах, такой режим может быть реализован на целевой плате. В будущем, излучение на четырех частотах одновременно позволит еще больше повысить временное разрешение зондирования ионосферы. Главной проблемой выступает возможность передатчика излучить 4 частоты одновременно без искажения. Это будет проверено в бедующей работе.

Таким образом, использование AD9959 в сочетании с ПЛИС-управлением открывает новые возможности для высокоскоростного зондирования ионосферы с минимальными временными задержками.

#### **Заключение**

В статье представлены узлы PCI-управляемых устройств для памяти SDRAM и синтезатора частот. Готовые узлы в последующих работах будут модернизированы, адаптированы и включены в общую прошивку (HDL-код) управляющей платы ионозонда. Также на основе полученных результатов будет повышаться рабочая частота за счет оптимизации критических путей в проекте. Для DDS синтезатора сделаны все блоки, реализующие быстрое переключение частот, а также были реализована встроенная RAM-память, оптимизирующая загрузку частот синтезатора в данном ионозонде.

#### **Благодарности**

Работа выполнена за счет средств субсидии, выделенной в рамках государственной поддержки Казанского (Приволжского) федерального университета в целях повышения его конкурентоспособности среди ведущих мировых научно-образовательных центров.

#### **Список литературы**

1. Всё о синтезаторах DDS (Компоненты и технологии). – 2025. – URL: <https://kit-e.ru/vsyo-o-sintezatorah-dds/> (дата обращения 01.05.2025).

2. IS42S16320D device's datasheet. – 2015. – URL: <https://static.chipdip.ru/lib/415/DOC012415159.pdf> (дата обращения 01.05.2025).

3. Реализация контроллера SDRAM (Habr). – 2025. – URL: <https://habr.com/ru/articles/737384/> (дата обращения 01.05.2025).

4. AD9959 device's datasheet. – 2017. – URL: <https://www.micro-semiconductor.com/datasheet/e1-AD9959BCPZ.pdf> (01.05.2025).